www.acsami.org

## Correction to ZnO/NiO Diode-Based Charge Trapping Layer for Flash Memory Featuring Low Voltage Operation

Chergn-En Sun, Chin-Yu Chen, Ka-Lip Chu, Yung-Shao Shen, Chia-Chun Lin, and Yung-Hsien Wu\* ACS Appl. Mater. Interfaces 2015, 7, pp 6383–6390. DOI: 10.1021/am507535c

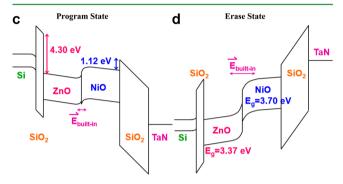

Recently, we found that in Figure 3c, d, the band diagram for program and erase operation, respectively, were

**Figure 3.** Band diagram for memory devices with ZnO/NiO charge trapping layer biased at (c) positive gate voltage and (d) negative gate voltage.

mistakenly uploaded. The band diagram of the charge-trapping layer ZnO/NiO should be switched so that the diagrams can be consistent with the operation mechanism described in the paper. The corrected band diagrams are shown below. The conclusions of the paper are not influenced by this change.